|

< Previous: (

Transport Overhead )

Table of Contents

Next: ( Pointer Processing ) >

Before getting into Synchronous

Payload Envelope (SPE), I feel its better to know about scrambling.

Every add/drop multiplexer sample

incoming bits according to a particular clock frequency. Now this clock

frequency is recovered by using transitions between 1s and 0s in the

incoming OC-N signal. Suppose, incoming bit stream contains long strings

of all 1s or all 0s. Then clock recovery would be difficult. So to enable

clock recovery at the receiver such long strings of all 1s or 0s are

avoided. This is achieved by a process called Scrambling.

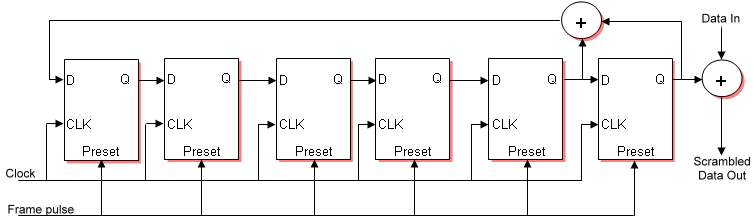

Scrambler is designed as shown in

the figure-5 below.

Figure-5

It is

a frame synchronous scrambler of sequence length 127. The generating

polynomial is 1+x6+x7. The scrambler shall be reset

to �1111111� on the most significant byte following Z0 byte in the Nth

STS-1. That bit and all subsequent bits to be scrambled shall be added,

modulo 2, to the output from the x7 position of the scrambler,

as shown in Figure 5.

The

framing bytes A1 and A2, Section Trace byte J0 and Section Growth byte Z0

are not scrambled to avoid possibility that bytes in the frame might

duplicate A1/A2 and cause an error in framing. The receiver searches for

A1/A2 bits pattern in multiple consecutive frames, allowing the receiver

to gain bit and byte synchronization. Once bit synchronization is gained,

everything is done, from there on, on byte boundaries � SONET/SDH is byte

synchronous, not bit synchronous.

An

identical operation called descrambling is done at the receiver to

retrieve the bits.

|